![[PukiWiki] [PukiWiki]](image/pukiwiki.png)

![[PukiWiki] [PukiWiki]](image/pukiwiki.png)

2009/05/01からのアクセス回数 11620

実際にプログラミングしてみると雑誌や本に書かれていないことがわかるものです。

今回は、

のがよいことが分かりました。(とてもいい収穫でした)

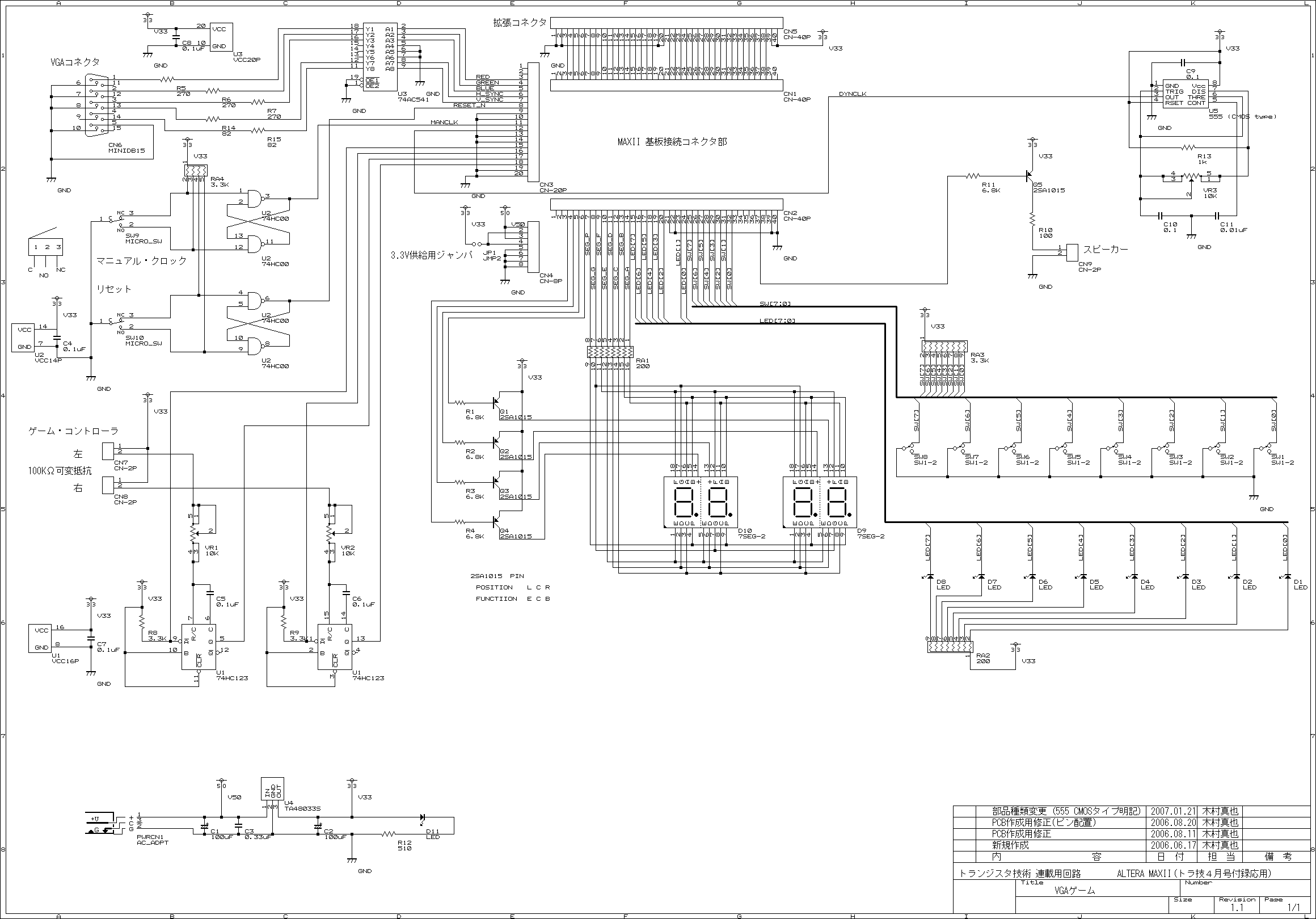

トランジスタ技術2006年4月付録のMAX IIと12月号から連載された「実験で学ぶロジック回路設計」 の教材だったHDL-CQ1を使ってCPLDのプログラミングをしてみます。

特集では、

の順で説明していますので、それにそって試してみます。

HDL-CQ1では、SELECTOR信号で7セグメントLEDを切り替えているため、 特集の第4章の例題は1個の7セグメントLEDを使うようにしました。

写真は、MANCLKのスイッチでカウントアップしている途中の様子です。

AlteraのQuartus II の最新のver.9.1は、Windows2000をサポートしていないので、開発環境ではVM Ware上にVer.7.1をインストールしました。

Ver.8.1より以前のQuartus IIではMacアドレスを送ってライセンスをAlteraから取得しますので、VM Ware のMacアドレスを固定にする必要があります。

VMイメージのvmxファイルをテキストエディタで開いて、以下の行を追加・変更します。

ethernet0.addressType = "static" ethernet0.address = "00:50:56:00:43:88"

Macアドレスは、00:50:56までは固定で、残りは自由に設定してもよいそうです。

また、以下のツールもインストールしました。

回路図の書き方は、特集の記事にそってButtonCount_topを以下のように書きました。

コネクタの配置は、

を参照し、以下のようにピンの配置をしました。

&(ping_setting.jpg);

この記事は、

皆様のご意見、ご希望をお待ちしております。